Enter " quartus_pgm -l" to find out your cable name. You may need to change your cable name to the one that's connected to your machine. output_files/axi4-tlm.sof' - Programs your board. $ quartus_pgm -c 'USB-Blaster ' -m jtag -o 'p. Here's an explanation of what the synthesis script ( synthesise.sh) does: $ quartus_sh -flow compile axi4-tlm - Runs the whole Quartus synthesis, place-and-route, and design assembly flow. You can run the Quartus synthesis flow by supplying the following at the Unix prompt (assuming you are in " trunk"): $ cd workspace/quartus To use the synthesis sources, look under the rtl/quartus-synthesis folder. Design verified on an Altera FPGA, and hardware measurements matches well with ModelSim simulations. I had to hack Quartus synthesis by changing some VHDL-2008 constructs to VHDL-93.

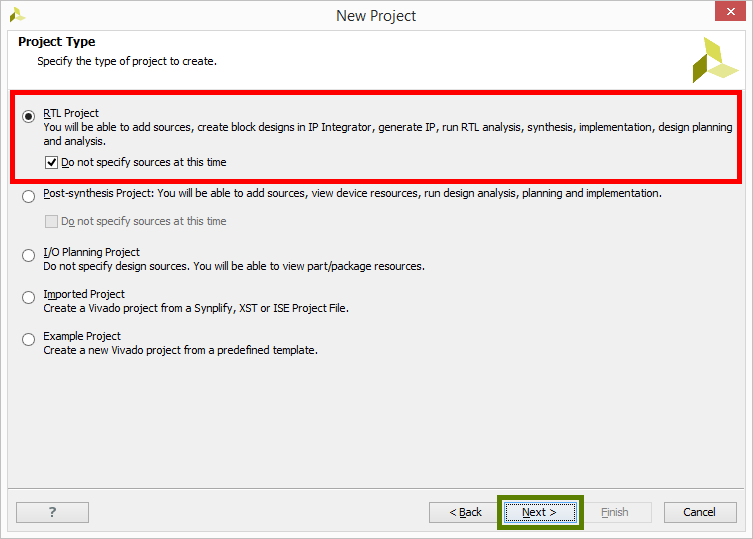

#ADD A VIVADO PROJECT TO SYNPLIFY PRO UPDATE#

Update : Design debugged on Altera Quartus. If you are using Synplify, or any other synthesis tool, let us know how well this core works with your toolchain. However, I believe Synopsys Synplify should be able to synthesise this. If you are using this simulator, or any other simulator, kindly let us know.Īltera and Xilinx tools failed to synthesise this core as is, as they do not yet support many of VHDL-2008 and VHDL-2002 language constructs. I tried simulating this on Synopsys VCS-MX, but the tool didn't like the VHDL-2008 constructs I was using very much. Email me at if you need help with simulating this project on Windows, and I will send you separate instructions.

If you have ModelSim/QuestaSim installed, the GUI will appear immediately after you run the script.Ĭurrently, I provide only the simulation script for Linux/Unix. Simply cd into the testbench/questa folder, and execute simulate.sh from the Unix prompt: $. To find out more about the cool features of OS-VVM, or to contribute to the project, visit the OS-VVM website.Īfter unpacking OS-VVM, we can now simulate the design with Mentor Graphics Questa/ModelSim. I do not adapt nor make any changes to the OS-VVM packages.

I have included OS-VVM verbatim from their website, so you will need to uncompress the file (you may uncompress using GUI as well): $ cd rtl/packages This separation between the high-level and low-level implementations results in a more modular and manageable design. The high-level transactions encapsulate the AXI4 protocol details in a lower-level layer known as the bus functional model. Communications is achieved simply by having a procedure-call statement in your sub-component. This enables sub-components of an SoC system to easily communicate with one another through the AXI4 bus.

#ADD A VIVADO PROJECT TO SYNPLIFY PRO FULL#

Currently, only the AXI4-Stream Master protocol is supported, but I also have plans to support AXI4-Lite and the full AXI4 protocols. This project implements the AXI4 transaction-level model (TLM) and bus functional model (BFM) in VHDL.

0 kommentar(er)

0 kommentar(er)